# Implementation of Binary FFT Using Cordic Algorithm

**R.Merlin Princy** PG Scholar, PSNACET, Dindigul, Tamilnadu, India.

S.Arun Kumar Assistant Professor, PSNACET, Dindigul, Tamilnadu, India.

Abstract - The Fast Fourier transform (FFT) is one of the most significant algorithms in Digital Signal Processing. It is habituated to compute the Discrete Fourier Transform (DFT) efficiently. In order to enhance the high performance and real-time requirements of modern applications. This paper offer a new type of hardware architecture is called Binary FFT using specific rotation.The suggested architecture is based on the radix-2 FFT algorithm only half of the samples at each must be rotated.CORDIC algorithm habituated to reckon sine and cosine functions and a prototypical computer implementation. This algorithm is used to reckon rotation factor to deduce a figuring cost and area. Develop the binary version of FFT, in order to deduce processing overhead. This architecture has been coded in Verilog and simulated by using Xilinx software.

Index Terms – Commutator, Coordinate Rotation Digital Computer (CORDIC), Rotator, Processing element (PE).

# 1. INTRODUCTION

The Fast Fourier transform (FFT) is one of the most momentous algorithms in Digital Signal Processing. It is habituated compute the Discrete Fourier Transform (DFT) efficaciously. In order to enhance the performance and real- time modern applications. The designers were tried to execute the efficacious architectures for the computation of the FFT. The pipelined architectures are widely evolved, because it furnish high throughput, low latency, low area and power consumption.It is suitable for some application such as Animation, Graphics, Image processing. There are two types of pipelined FFT. Serial pipelined & Parallel pipelined. Serial FFT, it enforce single instruction per clock cycle and Parallel FFT, it enforce several instruction per clock cycle. The FFT architectures are depicted by their loops, i.e., Feedforward or Feedback architectures, some outputs of the Feedback.In butterflies are fed back to the memories. It can be divided into Single path Delay Feedback (SDF)[2], which process a continuous flow of sample per clock one cycle, and Multipath Delay Feedback (MDF) [3], which process several samples in parallel. The feedforward architectures also known as Multi-path Delay Commutator (MDC), it does not have feedback loops and each stage proceed the processed data to the next stage. The butterfly stages are habituated to get the output [1]. The hardware tools are reduced, hence the gate

levels are optimized [5]. It habituates minimum amount of butterflies and memory by the use of rotator. The iterated values are stored in memory element[13]. It is a trade-off among butterflies, rotators and memoryThese architectures can also process several samples in parallel. In prevalent real- time interpretation requirements appear in employment, high anonymous applications such as Orthogonal Frequency Division Multiplexing (OFDM) and Ultra Wide Band (UWB).

# 2. RELATED WORKS

FFT is a way to evaluate Discrete Fourier transform result as more quickly. Fourier analysis is conversion of signal from time domain to frequency domain.It reduce the complexity of evaluating the DFT from  $O(n^2)$  to  $O(n \log n)$ . The Cooleytukey is a conquer algorithm that recursively breakdown a DFT. The N-point DFT of an input sequence x[n] is defined as,

| $X(k) = WN^{kn}$            | (1) |

|-----------------------------|-----|

| $W_N kn _{-e} - j2\pi kn/N$ | (2) |

$WN^{kn} = e^{-j2\pi kn/N}$

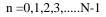

Figure 1.1 8 Point DIF FFT

There is two main expostulation can be distinguished. One is to calculate the FFT of multiple self-reliant data sequence. The FFT processors can participate the rotation recollection in order to demote the hardware. Second is to evaluate the FFT when several samples sequence are received in parallel. It is terminated when the essential throughput is higher than the clock to frequency of the device. It is essential to resort FFT architectures. CORDIC (Coordinate Rotation Digital Computer), is an arithmetic algorithm for efficicacious estimation of various transcend, Logarithmic, Exponential and trigonometric has been integrated in several arithmetic functions. It processors. Lately, it has been functioned to articulate and enforce in modern Digital Signal Processing (DSP) algorithms which require the estimation of sophisticated number multiplications, fundamental plane rotation. The Discrete Fourier Transform (DFT) is one of the most reckoning acute operation in Image compression. It has been used to Multimedia application.It is embraced in many standards such as JPEG, MPEG and H.264.

A disparate characteristic of the CORDIC algorithm habituates a sequence of fundamental rotations to realize a variety of sophisticated, nonlinear fundamental rotation require two simple shift-and-add operations to execute. It will reduces the latency (time between the attainable of input data and output), as well as hardware cost.

# 3. THE SERIAL COMMUTATOR OF FFT

The serial commutator (SC) FFT is based on the circuits for bitdimension permutation of serial data. It habituates a novel data management. This Process is based on radix-2 FFT algorithm and only half of the samples at each stage must be rotated.

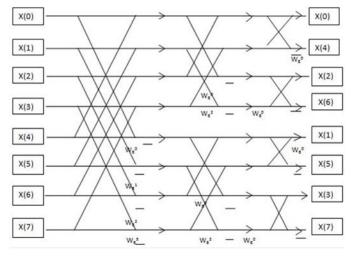

Figure 2.1 Processing Element of FFT

The processing element consist of butterfly and rotator. The radix-2 FFT architecture process one sample per clock cycle.It require only a complex adder and half a rotator per stage. The insignificant rotations are conveyed by rotators. The generic rotators are represented by a circle. Both butterflies and rotators are marked with N/2 . From that it require half of the components in butterflies and rotators.

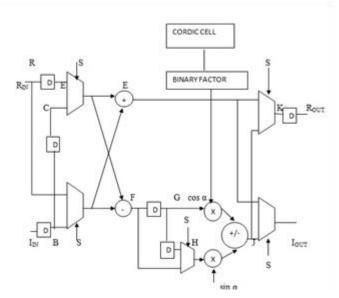

#### A.Butterfly

The butterflies uses a real adder and real subtractor instead of complex arithmetic operation.By using the twiddle factor ,it evaluate the real and imaginary value of binary data.Twiddle factor values are varied fiom DIF and DIT.

Figure 2.2 Twiddle Factor

$$W_N^k = e^{-j2\pi kn/N} \tag{3}$$

$$\mathbf{A}^{\mathbf{I}} = \mathbf{A} + \mathbf{B} \tag{4}$$

$$B^{1} = (A-B) * WN^{k}$$

$$B Rotator$$

(5)

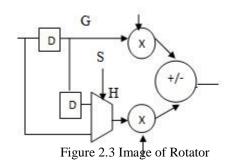

B.Rotatoi

The rotator is a term habituated to multiplexes the calculation in time.It require two real multipliers and one adder instead of four real multipliers and two adders. The half butterfly and half rotator form the processing element (PE) of the architecture.

# C. Data Management

The processing element evaluates a butterfly and a rotation on twain of data appear in sequential clock cycles. The data management of the SC FFT handled unperturbed in consecutive clock cycles. It transpire in all the stages of the FFT.

# 4. PROPOSED METHOD

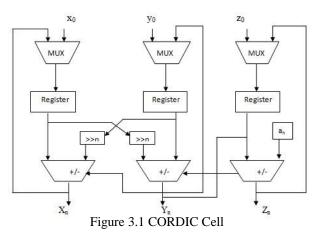

It stands for (Co-ordinate Rotation Digital Computer) also known as Volder's algorithm. It converge one bit per iteration. Pseudo multiplication and pseudo division is used, when there is no hardware is available . It require only addition, subtraction, bit-shift and table look up. Sometimes it referred as Digital Resolver. The rotation-mode CORDIC algorithm is to rotate a vector  $[U_X, U_y]$  through an angle to is given by,

$$(U_X)_{i+1} = (U_X)_i - \sigma_i (U_Y)_i \cdot 2^{-i}$$

(6)

$$(UY)_{i+1} = (UY)_{i+\sigma_i} (U_X)_{i,2}^{-i}$$

$$\tag{7}$$

$$\varphi_{i+1} = \varphi_i - \sigma_i \tan^{-1}(2^{-1})$$

(8)

It operates at two modes Rotation mode and Vectoring mode.In fixed rotation, it could be already executed and the sign-bits corresponding  $(\phi_i)$  to might be stored in a sign-bit register (SBR) in CORDIC circuit [9]. The CORDIC circuit is not to the remaining angle during the necessary evaluate CORDIC iterations. CORDIC circuit for fixed rotations are corresponding to X and Y are fed as set/reset input to the twain of input registers and the successive feedback values X I and Y I at the iteration are fed in parallel to the input registers. The angle values are calculated using the CORDIC cell for required iteration. The angle values are fed to the Rotator through Binary factor for binary information. The data are processed and the output is received in Rout for real value and Iout for imaginary value. The conventional victual the pair of input registers with the initial values and as well as the feedback values are through a pair of multiplexers.

#### 5. EXPERIMENTAL RESULT

The suggested fault compensation circuit with fixed width multiplier are simulated by using Xilinx ISE 12.1 and enforced in spartan-6 FPGA processor. During the execution, the parameters are taken from the synthesis report. The input is purely based on 0's and 1's. The experimental results are shown in table.

Table 1. Experimental result

| s.no                    | Parameter | Existing | Proposed |  |  |  |

|-------------------------|-----------|----------|----------|--|--|--|

| 1                       | SLICE     | 9        | 6        |  |  |  |

| 2                       | LUT       | 16       | 7        |  |  |  |

| 3                       | IOB       | 18       | 14       |  |  |  |

| 6. PERFORMANCE ANALYSIS |           |          |          |  |  |  |

The interpretation of the suggested equatorial fault compensation with the subsisting scheme fixed width RPR are analyzed based on the area and fault compensation which was given below. The optimistic values are enforced better than the subsisting system. The proposed algorithm reduces area, power, look up table values and input output blocks.

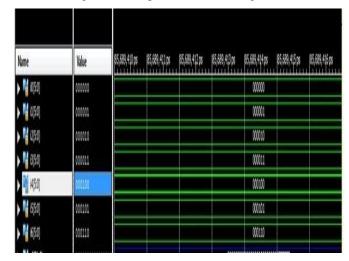

# 7. SIMULATION RESULT

The simulation results are obtained from the Xilinx software. The coding are developed for the impementation of CORDIC, implementation of FFT and implementation of CORDIC with FFT. The synthesized reports are compared to the previous method.

| Name                | Value                                   | e1 11 | 1999,993 ps | 999,994 ps        | 999,995 ps          | 999,996 ps                              | 999,997 ps         | 999,998 ps |

|---------------------|-----------------------------------------|-------|-------------|-------------------|---------------------|-----------------------------------------|--------------------|------------|

| l <mark>e</mark> v  | Z                                       |       |             |                   |                     |                                         |                    |            |

| 🌡 deg               | 0.055900                                |       |             |                   |                     | 0.055900                                |                    |            |

| 15 two              | 0.000900                                |       |             |                   |                     | 0.000900                                |                    |            |

| ▶ 👹 x(7:0] /fvc/two | [1.316237,1.2988                        |       |             | [1.316237,1.29    | 98815,1.328469,1.36 | 6425,1.214600,1.21                      | 4600,0.607300,0.60 | 7300]      |

| ▶ 10 y[7:0]         | [0.516894,0.5574                        |       |             | [0.516894,0.5     | 57482,0.474453,0.3  | 3650,0.607300,0.00                      | 0000,0.607300,0.0  | 0000]      |

| 🕨 😽 z[7:0]          | [-1.431200,-3.22                        |       |             | [-1.431200,-3.221 | 100,0.346200,7.471  | 200,-6.565000,20.00                     | 0000,-25.000000,2  | 0.000000]  |

| 16 sign             | -1.000000                               |       |             |                   |                     | -1.000000                               |                    |            |

| 16 զ                | X                                       |       |             |                   |                     |                                         |                    |            |

| 🔻 👹 i[31:0]         | 000000000000000000000000000000000000000 |       |             |                   | 00000000000         | 000000000000000000000000000000000000000 | 1011               |            |

| 16 [31]             | 0                                       |       |             |                   |                     |                                         |                    |            |

| [30]                | 0                                       |       |             |                   |                     |                                         |                    |            |

| 16 [29]             | 0                                       |       |             |                   |                     |                                         |                    |            |

| 16 [28]             | 0                                       |       |             |                   |                     |                                         |                    |            |

Figure 6.1 Output of CORDIC Algorithm

Figure 6.2 Output of FFT

| 1 |                     | 000000 | 000000 |   |  |  |  |   |

|---|---------------------|--------|--------|---|--|--|--|---|

|   |                     | 000001 | 000001 | 2 |  |  |  |   |

|   |                     | 000010 | 000010 |   |  |  |  |   |

|   |                     | 000011 | 000011 |   |  |  |  |   |

|   |                     | 000100 | 000100 |   |  |  |  |   |

|   |                     | 000101 | 000101 |   |  |  |  |   |

|   |                     | 000110 | 000110 |   |  |  |  |   |

|   | 🖶 🔶 /fft/i7         | 000111 | 000111 |   |  |  |  |   |

|   |                     | 0      | 0      | ġ |  |  |  |   |

| ľ |                     | 1      | 1      |   |  |  |  |   |

|   |                     | 2      | 2      |   |  |  |  | j |

|   |                     | 3      | 3      |   |  |  |  | j |

|   |                     | 4      | 4      |   |  |  |  |   |

|   | <b>₽-</b> ∲ /fft/x5 | 5      | 5      |   |  |  |  |   |

|   | <b>⊞-</b> ∲ /fft/x6 | 6      | 6      |   |  |  |  |   |

|   |                     | 7      | 7      |   |  |  |  |   |

|   | ₽-�/fft/s10         | 4      | 4      |   |  |  |  |   |

|   | ₽                   | -4     | -4     |   |  |  |  |   |

|   | <b></b> ↓ /fft/s12  | 8      | 8      |   |  |  |  |   |

|   | ∎                   | 4      | -4     |   |  |  |  |   |

|   | ₽-� /fft/s14        | 6      | 6      |   |  |  |  |   |

|   | ₽                   | -4     | -4     |   |  |  |  |   |

|   | ₽-� /fft/s16        | 10     | 10     |   |  |  |  |   |

|   |                     | -4     | -4     |   |  |  |  |   |

Figure 6.3 Output of FFT with CORDIC Algorithm

#### 8. CONCLUSION

This paper has presented the Binary FFT architecture. It is the first FFT used to compute the value of output sequencs using CORDIC algorithm. It creates a data management that allows for using the theoretical minimum amount of hardware resources for a Binary FFT. Compared to previous designs, the presented Binary FFT reduces either the number of rotator, or the number of adders or the memory of the design. A solution for natural I/O has also been presented, which offers comparable results to previous natural I/O FFTs. The experimental results obtained to verify the architecture, leading to small area and low power consumption.

#### REFERENCES

- "Design of Multipath Delay Commutator Architecture Based FFT Processor for 4<sup>th</sup> Generation System", A.Amjadha, E.Konguvel, J.Raja, International Journal of Computer Applications, Volume 89 - No 12, March 2014.

- [2] "Hardware Implementation of DIT FFT", U.Akshata, I.Hameem Shanavas, D.Gopika, MIT International Journal of Electronics and Communication Engineering, Vol. 3, No. 1, Jan. 2013.

- [3] "Area Efficient Pipelined Radix-2<sup>k</sup> Feedforward FFT Using Booth Multiplier", Jampa Shravani, K.Siva Nagi Reddy, International Journal of VLSI System ISSN 2322-0929, Vol.02, October-2014.

- [4] "Optimum Circuits for Bit Reversal", Mario Garrido, Jesus Grajal, Oscar Gustafsson, IEEE Transaction on circuits and system II. Vol. 58, NO.10, Oct 2011.

- [5] "Power and Optimization for Pipelined CORDIC Architecture in VLSI", G.Sandhya, Syed Inthiyaz, Dr. Fazal Noor Basha, International Journal of Engineering Research and Applications Vol. 2, May-Jun 2012, page.1588- 1595.

- [6] "Modified Scaling Free CORDIC based Pipeline MDC FFT&IFFT for Radix 2<sup>2</sup> Algorithm", C.Paramasivam, K.B.Jeyanthi, IEEE Transaction on VLSI,May 2013.

- [7] "Efficient CORDIC Algorithms and Architectures for Low Area and High Throughput Implementation", Leena Vachhani, K. Sridharan, Pramod K. Meher, IEEE Transactions on Computers, 57(8):1148–1152, 2008.

- [8] "A Hybrid-Radix Approach for Efficient Implementation of Unfolded CORDIC Architectures for FPGA Platforms", Burhan Khurshid, Roohie Naz Mir, Animesh Kumar, Shatish Kumar, International Conference on Signal Processing and Integrated Networks, 2014.

- [9] "CORDIC Design for Fixed Angle Rotation", Pramod Kumar Meher, Sang Yoon Park, IEEE Transactions on Very Large Scale Integration Systems, VOL. 21, NO. 2, February 2013.

- [10] "An Efficient implementation of rotational radix-4 CORDIC based FFT processor", A.Yasodhai, A.V.Ramprasad, Intelligent Computational Systems (RAICS), 2013 IEEE Recent Advances, February 2014.

- [11] "FPGA implementation of Radix-2 FFT processor based on Radix-4 CORDIC", <u>E.Joseph, A.Rajagopal, K.Karibasappa, International</u> <u>Conference</u> December 2012.